## University of California College of Engineering Department of Electrical Engineering and Computer Sciences

E. Alon

Thursday, December 20, 2007. 12:30-3:30pm

# EECS 141: FALL 2007—FINAL EXAM

For all problems, you can assume the following transistor parameters (unless otherwise mentioned):

## **NMOS:**

$$V_{Tn} = 0.4$$

,  $k'_n = 115 \,\mu\text{A/V}^2$ ,  $V_{VSAT} = 0.6 \,\text{V}$ ,  $\lambda = 0$ ,  $\gamma = 0.4 \,\text{V}^{1/2}$ ,  $2\Phi_F = -0.6 \,\text{V}$

$$V_{Tp} = -0.4 \text{ V}, k'_p = -30 \text{ } \mu\text{A/V}^2, V_{VSAT} = -1 \text{ V}, \lambda = 0, \gamma = -0.4 \text{ } V^{1/2}, 2\Phi_F = 0.6 \text{ V}$$

(11.

|         | Last Jointions | First |                    |    |

|---------|----------------|-------|--------------------|----|

| GRAD/UN | DERGRAD        |       |                    |    |

|         |                |       | <b>Problem 1:/</b> | 16 |

|         |                |       | <b>Problem 2:/</b> | 21 |

|         |                |       | <b>Problem 3:/</b> | 22 |

|         |                |       | <b>Problem 4:/</b> | 16 |

|         |                |       | <b>Problem 5:/</b> | 14 |

|         |                |       |                    |    |

Total: \_\_\_\_\_/ 89

## PROBLEM 1: SRAM Design (16 pts)

In this problem, we will be looking at a 256 x 256 SRAM, where each 6T cell is 4µm wide and 3µm tall. All of the devices in the SRAM cell are minimum length (L = 0.25µm), and you can assume that both the NMOS access transistors and the NMOS pull-down transistors are 0.5µm wide. You can also assume that when  $V_{DD} = 2.5V$ , the transistors have  $C_G = 2fF/\mu m$ ,  $C_D = 1fF/\mu m$ , and  $R_{sqn} = R_{sqp}/2 = 15k\Omega/\square$ .

a) (2 pts) For  $V_{DD}$  = 2.5V, what is the total capacitance loading each bitline in this memory? You can assume that the bitline wire has a capacitance/length of 0.15fF/ $\mu$ m.

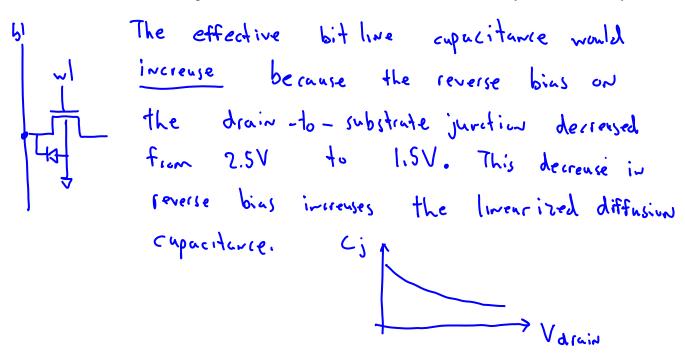

**b)** (3 **pts**) If the supply voltage of the SRAM was reduced to 1.5V, would the effective capacitance on the bitlines increase, decrease, or stay the same? Why?

c) (4 pts) Given your answer to part a) (i.e.,  $V_{DD} = 2.5V$ ), and assuming that the delay of the final stage in the decoder is 100ps, what is the delay (in ns and including the slope effect) from the wordline rising to the bitline falling?

d) (4 pts) If the memory operates at 100MHz, how much dynamic power is dissipated due to switching the 256 bitlines? You can assume that the bitlines swing all the way from 0V to  $V_{\rm DD}$ .

e) (3 pts) Now we'll look at whether we can save some power by adding sense amps to this design. If the sense amps would dissipate 10% of the power you calculated in part d), but the bitlines now swing only between 2V and  $V_{DD}$  (=2.5V), will adding sense amps reduce the power of the SRAM? If so, by how much?

#### PROBLEM 2: Logical Effort and Transistor Models (21 pts)

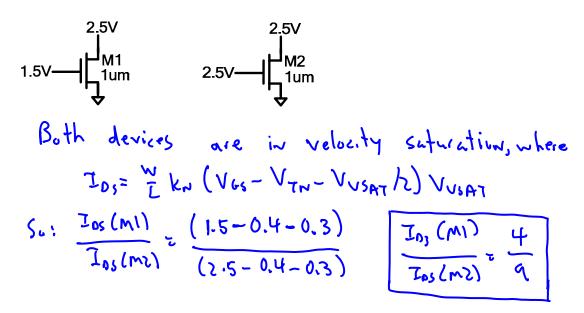

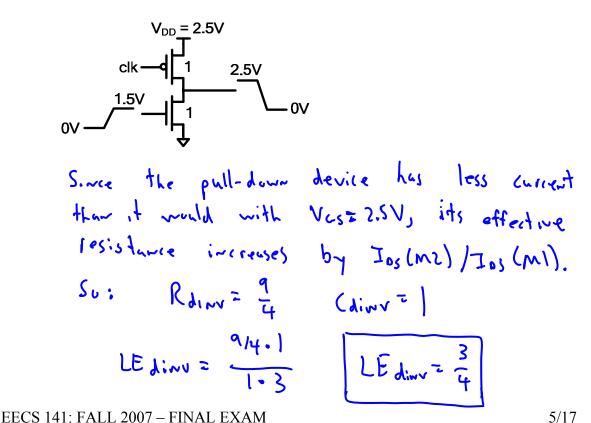

a) (3 pts) Using the unified transistor model, what is the ratio of drain currents for the two  $0.25\mu m$  long transistors shown below? I.e., what is  $I_{DS}(M1)/I_{DS}(M2)$ ?

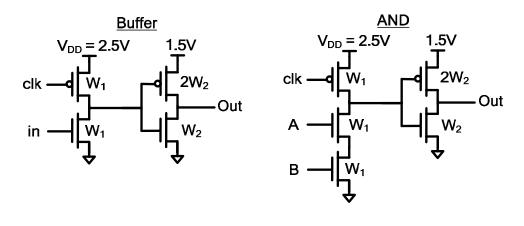

**b)** (4 pts) Shown below is a dynamic (unfooted) inverter where the input to the inverter swings only between 0V and 1.5V, while the power supply for the dynamic inverter is 2.5V. During evaluation, what is the logical effort of this dynamic inverter relative to a standard inverter with  $W_p = 2W_n$  and VDD = 2.5V? (Hint: your answer to part a) is directly related to this problem.)

c) (6 pts) Now we'll look at the static inverter (shown below) that would drive the dynamic inverter we just looked at. Once again comparing to a standard inverter with a supply voltage of 2.5V, what is the logical effort of this inverter for the rising transition at the output? (Hint: What is the effective resistance of the PMOS transistor?)

Renember that R

$$\propto \frac{V_{DD}}{I_{DSRT}}$$

So, the relative resistance of the PMOS device is set by:

$$R_{PROS} = \frac{1.5V}{I_{DSRTP}(1.5V)} / \frac{2.5V}{I_{DSRTP}(2.5V)}$$

Remos =  $\frac{1.5V}{2.5V} \cdot \frac{(2.5V - 0.4V - 0.5V)}{(1.5V - 0.4V - 0.5V)} = \frac{1.5}{2.5} \cdot \frac{1.6}{0.6} = 1.6$

Since the input repactitude is the same, the LE is just the calio of resistance:

d) (8 pts) Let's now look at building chains of logic using such "alternating supply" domino gates (as shown below). Assuming your answer to part b) was  $LE_{dinv} = 0.75$  and to part c) was  $LE_{inv} = 1.5$ , what is the EF/stage you should target to minimize the delay of a chain of these gates?

Just like normal domoro gutes, we first have to find the effective LE of our furtist buffer. In this case:

So, the optimen EF/stage is:

# **PROBLEM 3: Sequential Elements (22 points)**

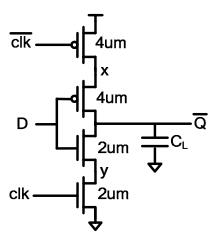

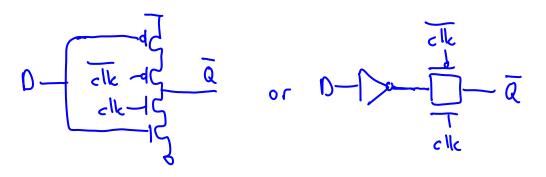

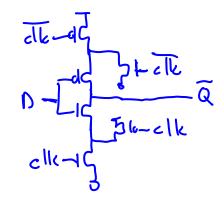

In this problem we will be examining the latch shown below, which has been implemented out of a tri-state inverter. Throughout this problem, you can assume that  $V_{DD}=2.5V,\,C_G=2fF/\mu m,\,C_D=2fF/\mu m,\,and\,R_{sqn}=R_{sqp}/2=15k\Omega/\square$ .

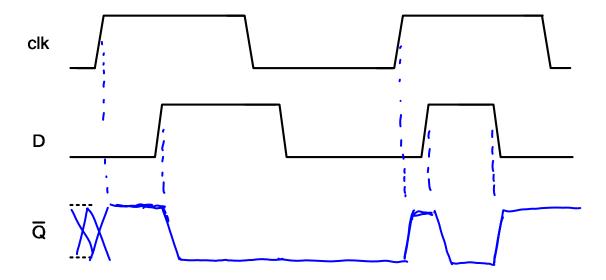

a) (2 pts) Assuming the latch is ideal (i.e., has no delay, zero setup/hold time, etc.), fill in the waveform for  $\overline{Q}$  given the clock and data inputs shown below.

**b)** (6 pts) For  $C_L = 50$ fF and assuming  $\overline{Q}$  is initially charged to  $V_{DD}$  and y is initially 0V, what is the  $t_{clk-q}$  of this latch when D=1? You should assume that clk is a ramp.

c) (4 pts) One of your fellow designers comes to you one day and says that when she used this latch in her circuit with  $C_L = 5 f F$ , the latch failed to function correctly. More specifically, if D transitioned, the inverter receiving the output of the latch would transition even when clk was low. However, you have verified that the latch functions correctly when  $C_L = 50 f F$ . What is the cause of the error when the latch has a small  $C_L$ ? (Hint: Think about the second transition of D)

The cause of this error is charge sharing. For example, or the second transition of D, x was previously charged to 2.5V while Q is at OV (and should remain there). However, when D goes for and connects x to Q, the voltage would rise well above Voo/2 (because (x) 6 µm. CD+ 5FF)

d) (6 pts) What is the minimum load capacitance required for the latch to function correctly? You can assume that the inverter receiving the output of the latch has an ideal VTC with a switch point  $V_{sw} = V_{DD}/2$ , and that none of the transistors' source/drain regions have been shared.

First, we need to fird the worst case for charge sharing.

$$C_{x} = 4\mu n. Co + 4\mu m. Co + 4\mu m. Co = 24ff$$

$$C_{y} = 2\mu n. Co + 2\mu m. Co + 2\mu m. Co = 12ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co + 2\mu m. Co = 12ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 2\mu m. Co = 12ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co + 2\mu m. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x} = 1 + 2\mu n. Co = 24ff$$

$$C_{x}$$

EECS 141: FALL 2007 – FINAL EXAM

e) (4 pts) Other than artificially increasing C<sub>L</sub>, how can you modify the latch to fix the problem you identified in part c)? You should explain your fix and draw a new transistor-level schematic of the latch (no sizing necessary). (Note that there is more than one possible fix – you will receive bonus credit for up to two additional fixes you identify and draw.)

Fix #1: Re-crhor the latch so that never get charge sharing when clk is low:

Fix #2: Pre-charge/discharge the intermediate nodes.

Fix #3: Keeper. Note that this fix is the loust fool-proof, surce the keeper could get flopped by the charge-sharing.

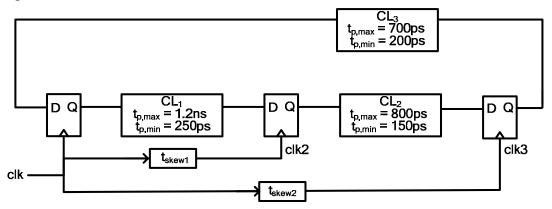

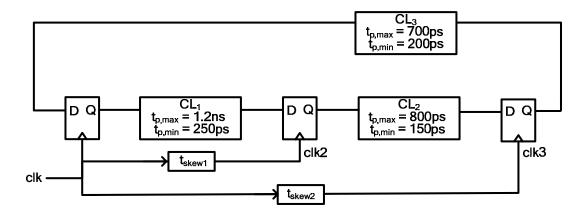

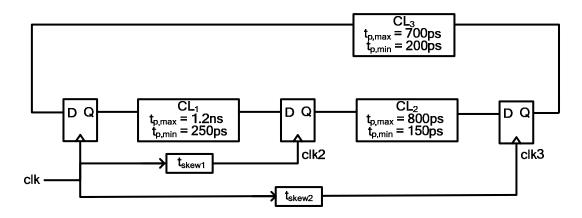

#### **PROBLEM 4: Timing (16 points)**

In this problem we will be examining the pipeline shown below. The minimum and maximum delays through the logic are annotated on the figure, and the flip-flops have the following properties:  $t_{\text{clk-q}} = 150 \, \text{ps}$ ,  $t_{\text{setup}} = 50 \, \text{ps}$ , and  $t_{\text{hold}} = 100 \, \text{ps}$ . You can assume that the clock has no jitter, but  $t_{\text{skew1}}$  and  $t_{\text{skew2}}$  can be either positive or negative.

a) (4 pts) What is the minimum clock cycle time if  $t_{skew1} = -100ps$  and  $t_{skew2} = 50ps$ ?

**b)** (4 **pts**) Assuming  $t_{skew2}$  is fixed at 50ps, how negative can  $t_{skew1}$  be before this pipeline (repeated above for your convenience) fails a hold-time constraint?

c) (8 pts) If you could intentionally set the values of t<sub>skew1</sub> and t<sub>skew2</sub>, what values would you choose in order to minimize the cycle time of this pipeline (again repeated above)? What would be the cycle time in this case?

#### **PROBLEM 5: Arithmetic Blocks (14 points)**

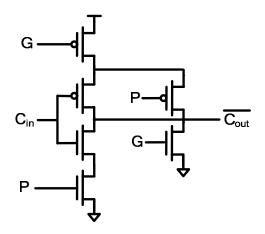

a) (3 pts) Shown below is a static CMOS implementation of a gate that computes the carry-out at a particular bit position. If the "P" signal that was fed into this gate was calculated using A + B (instead of  $A \oplus B$ ), would the output of this gate still be correct? Why or why not?

The only difference between A+B and A+B is when A=B=1. In this case, the OR version sets P=1, while the xor version sets P=0.

This gate implements Cout = G+P·Cin, and when A=B=I, G=I. So, in this case

Cont=I no matter what P is, and thus the output of the gate will be correct with either version of P.

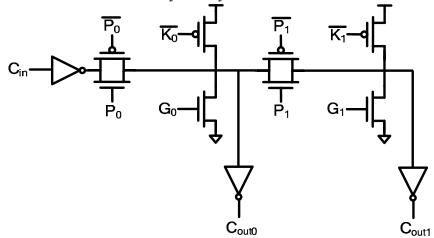

**b)** (**5 pts**) Now let's look at a the gate shown below that computes the carry-out for two bit positions, but this time implemented with a Manchester carry chain. Is this gate guaranteed to function correctly if the P signals that are fed to this gate are calculated as A + B? Why or why not?

Because we have used bidirectional push-gates, this time the gate will not function correctly for either version of P. Carender for example  $A_1 = B_1 = 1$  and  $A_0 = B_0 = 0$ . If the OR version of P is used, we will have  $P_0 = 0$ ,  $K_0 = 1$ ,  $P_1 = 1$ ,  $G_1 = 1$ , leading a drive fight between the  $G_1 = 1$  device.

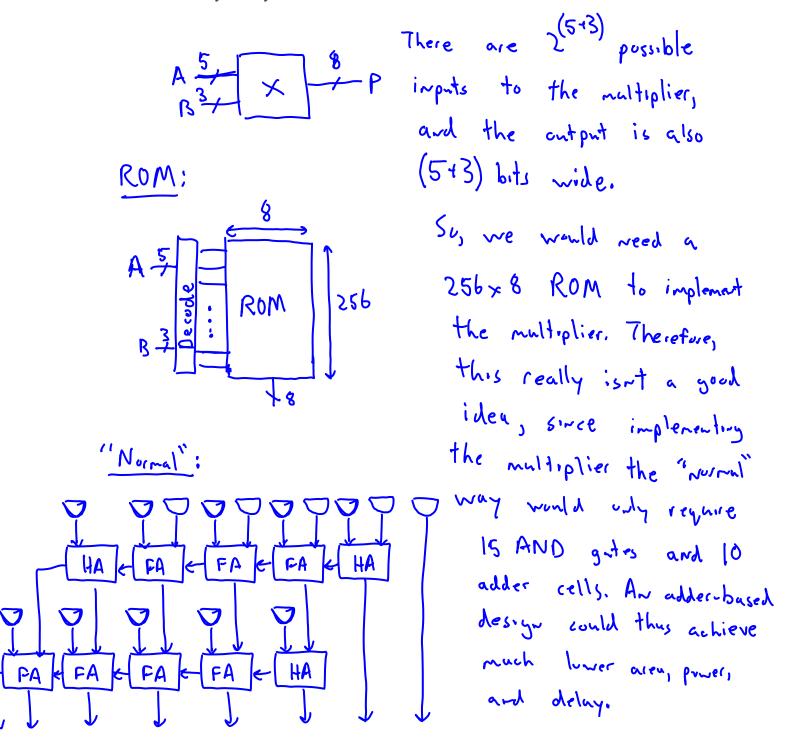

c) (6 pts) One of the designers at your company (who didn't take EE141) comes to you one day and says that he never understood the logic for multipliers, and proposes to build a multiplier out of a ROM instead of out of full-add and half-add cells. How large of a ROM would you need to implement a 5-bit by 3-bit multiplier? (You can quote your answer in terms of the number of rows and number of columns this ROM would need to contain.) Do you think this a good idea? Why or why not?